EducatioN & Experience

2018-2022

ruppin accademic center

BSC. Electrical Engineering, Cum Laude

2011-2013

COMPREHENSIVE SCHOOL FOR SCIENCE, HADERA

Associate Degree, Elctronics and Computer Engineering

Jan 2022 – Present

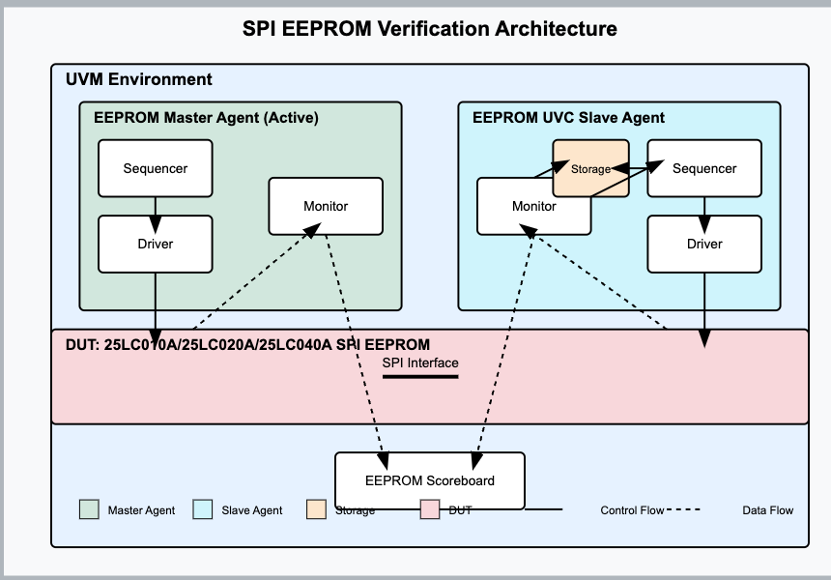

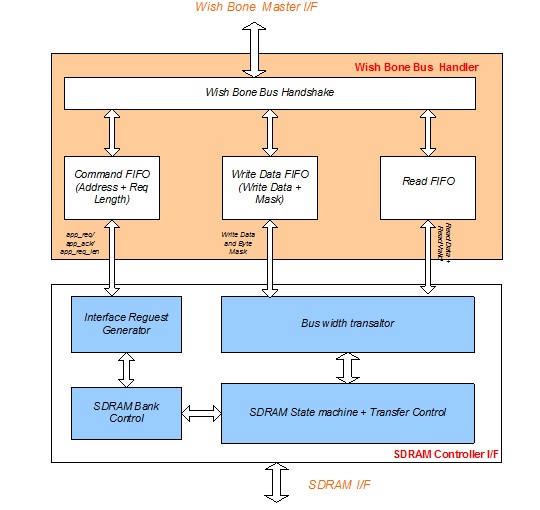

verification engineer -Microchip

- Took full ownership of developing and implementing comprehensive UVM-based verification environments from ground up, including verification strategy and execution plans.

- Created and executed verification plans for challenging digital blocks, achieving high coverage goals.

- Designed UVM-based VIP and UVC for custom protocols, accelerating verification cycles and tests’ run time.

Developed a Python GUI tool which shortened regression setup time by 70% and Coverage closure by 30%.

may 2021-jan 2022

Post-Silicon Validation Engineer – Microchip

Bridged pre-silicon and post-silicon verification efforts by correlating test results, improving model accuracy.

Gained deep system-level understanding through end-to-end validation of complex SoC designs

Developed automated test platforms using Python for comprehensive validation

Built robust test infrastructure by leveraging extensive hardware-software interaction knowledge

jan 2017 – apr 2021

Hardware Engineer – Niron Systems & Projects

Board design of tester circuits using Orcad Design Suite (Capture & Allegro).

Worked hands-on with cutting-edge systems, developing strong debugging and problem-solving skills

Developing Automatic Test Equipment. Developed a one-fits-all tester.

Automation Scripting

SoC and Block level Verification

Coverage Closure

Mixed Signal Verification

Digital Verification

UVM

hobbies etc.

Have a great idea?