AI is Reshaping Hardware Verification: Insights from Siemens’ Vision

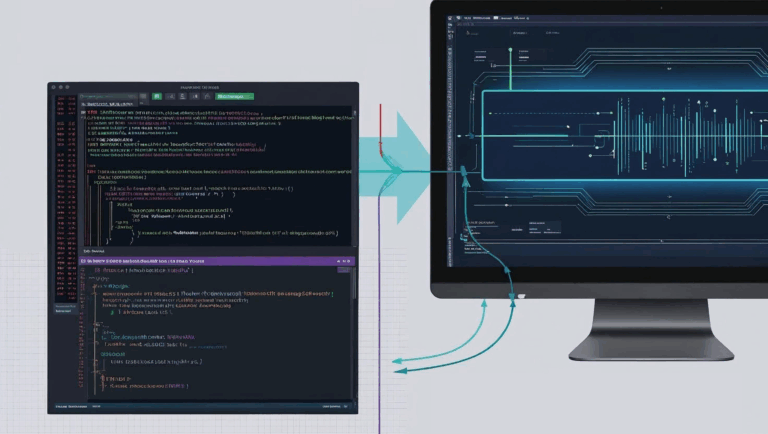

Discover how AI is transforming hardware verification in 2025, as discussed by Abhi Kolpekwar (VP at Siemens) on "The DV Digest" podcast. Explore the evolving role of verification engineers, the impact of artificial intelligence on EDA tools, and the real-world shift from hype to practical results in chip design and testing.